# ETSITS 101 548-1 V2.4.1 (2020-05)

Access, Terminals, Transmission and Multiplexing (ATTM);

European Requirements for Reverse Powering

of Remote Access Equipment;

Part 1: Twisted pair networks

Reference

RTS/ATTM-0636

Keywords

ADSL2plus, VDSL2

#### **ETSI**

650 Route des Lucioles F-06921 Sophia Antipolis Cedex - FRANCE

Tel.: +33 4 92 94 42 00 Fax: +33 4 93 65 47 16

Siret N° 348 623 562 00017 - NAF 742 C Association à but non lucratif enregistrée à la Sous-Préfecture de Grasse (06) N° 7803/88

#### Important notice

The present document can be downloaded from: <u>http://www.etsi.org/standards-search</u>

The present document may be made available in electronic versions and/or in print. The content of any electronic and/or print versions of the present document shall not be modified without the prior written authorization of ETSI. In case of any existing or perceived difference in contents between such versions and/or in print, the prevailing version of an ETSI deliverable is the one made publicly available in PDF format at <a href="https://www.etsi.org/deliver">www.etsi.org/deliver</a>.

Users of the present document should be aware that the document may be subject to revision or change of status.

Information on the current status of this and other ETSI documents is available at

<a href="https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx">https://portal.etsi.org/TB/ETSIDeliverableStatus.aspx</a>

If you find errors in the present document, please send your comment to one of the following services: https://portal.etsi.org/People/CommitteeSupportStaff.aspx

#### **Copyright Notification**

No part may be reproduced or utilized in any form or by any means, electronic or mechanical, including photocopying and microfilm except as authorized by written permission of ETSI.

The content of the PDF version shall not be modified without the written authorization of ETSI.

The copyright and the foregoing restriction extend to reproduction in all media.

© ETSI 2020. All rights reserved.

**DECT™**, **PLUGTESTS™**, **UMTS™** and the ETSI logo are trademarks of ETSI registered for the benefit of its Members. **3GPP™** and **LTE™** are trademarks of ETSI registered for the benefit of its Members and of the 3GPP Organizational Partners.

oneM2M<sup>™</sup> logo is a trademark of ETSI registered for the benefit of its Members and of the oneM2M Partners.

GSM® and the GSM logo are trademarks registered and owned by the GSM Association.

# Contents

| Intelle          | ectual Property Rights                                                                       | 6   |

|------------------|----------------------------------------------------------------------------------------------|-----|

| Forew            | vord                                                                                         | 6   |

| Moda             | l verbs terminology                                                                          | 6   |

|                  | uction                                                                                       |     |

|                  |                                                                                              |     |

| 1                | Scope                                                                                        |     |

| 2                | References                                                                                   |     |

| 2.1              | Normative references                                                                         |     |

| 2.2              | Informative references                                                                       | 8   |

| 3                | Definition of terms, symbols and abbreviations                                               | 8   |

| 3.1              | Terms                                                                                        |     |

| 3.2              | Symbols                                                                                      |     |

| 3.3              | Abbreviations                                                                                |     |

| 4                | Introduction to Reverse Power Feed                                                           | 11  |

| 5                | Reverse Power Feed Architecture                                                              |     |

| 5.1              | Basics of RPF                                                                                |     |

| 5.2              | Reverse Power Feed and POTS Co-Existence                                                     |     |

| 5.2.1<br>5.2.2   | Overview                                                                                     |     |

| 5.2.2<br>5.2.2.1 | 1                                                                                            |     |

| 5.2.2.1          |                                                                                              |     |

| 5.2.2.3          | •                                                                                            |     |

| 5.2.2.4          |                                                                                              |     |

| 5.3              | Reverse Power Feed Architecture without POTS on the same pair (RPFA-NOP)                     |     |

| 5.4              | Reverse Power Feed Architecture with Baseband POTS from the Exchange (RPFA-EXP)              | 15  |

| 5.5              | Reverse Power Feed Architecture with Baseband POTS from the Exchange Sharing the in-premises | 1.7 |

| 5.6              | Wiring (RPFA-EXPSW)                                                                          |     |

| 5.0<br>5.7       | Reverse Power Feed Architecture with Derived POTS (RFFA-DRF)                                 |     |

| 5.8              | Reverse Power Feed Architecture without POTS and with Broadband Bypass (RPFA-NOPBB)          |     |

| 6                | Reverse Power Feed Start-Up Protocol                                                         | 21  |

| 6.1              | Introduction                                                                                 |     |

| 6.1.1            | General                                                                                      |     |

| 6.1.2            | Start-up in presence of MELT signature                                                       |     |

| 6.2<br>6.2.1     | Metallic Detection based Start-Up (MDSU) Protocol                                            |     |

| 6.2.1            | Signature detection                                                                          |     |

| 6.2.3            | Start-up Sequence diagram                                                                    |     |

| 6.2.4            | Start-up flow chart                                                                          |     |

| 6.2.5            | POTS RCR Protocol (PRP) - Optional extension of MDSU                                         |     |

| 6.2.5.1          |                                                                                              |     |

| 6.2.5.2          |                                                                                              |     |

| 6.2.5.2          |                                                                                              |     |

| 6.2.5.2          |                                                                                              |     |

| 6.2.5.3<br>6.3   | Interoperability between "PRP capable" and "non PRP capable devices"                         |     |

| 6.3.1            | General                                                                                      |     |

| 6.3.2            | DGL pulse sequence                                                                           |     |

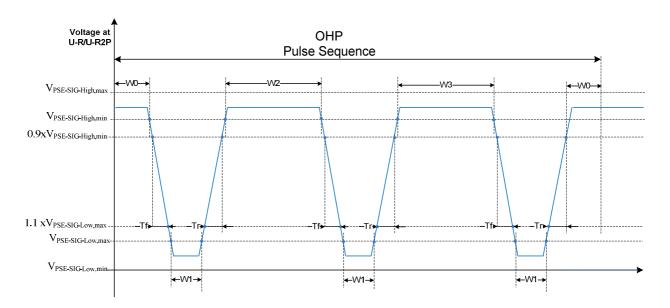

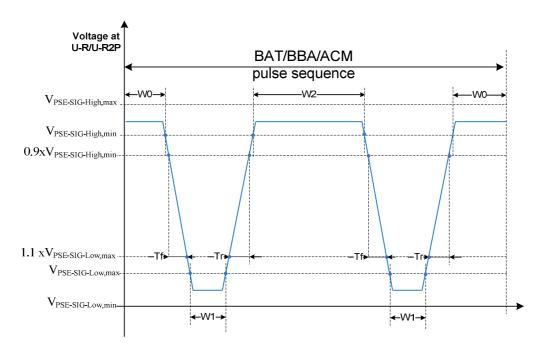

| 6.3.3            | OHP pulse sequence                                                                           |     |

| 6.3.4            | BAT, BBA and ACM pulse sequences                                                             | 42  |

| 6.4              | RPF Operations and Maintenance                                                               | 44  |

| 7                | Reverse Power Feed Characteristics                                                           | 45  |

| 7.1              | Safety Aspects                                                                               |     |

|                  |                                                                                              |     |

| 7.1.1          | Background                                                      | 45  |

|----------------|-----------------------------------------------------------------|-----|

| 7.1.2          | Unintended consequences                                         |     |

| 7.2            | RPF Range Options and Classes                                   |     |

| 7.3            | Electrical reference model and RPF Noise Limits                 |     |

| 7.4            | Zero touch DPU                                                  | 49  |

| 7.5            | PSE and DPU PE electrical specification                         | 52  |

| 7.5.1          | PSE electrical specification                                    | 52  |

| 7.5.1.1        | PSE electrical specification on interface U-R2P                 | 52  |

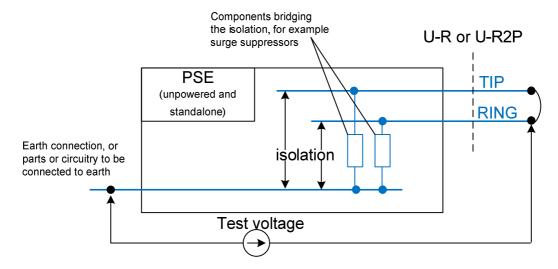

| 7.5.1.2        | PSE isolation requirements                                      | 54  |

| 7.5.1.3        |                                                                 |     |

| 7.5.1.4        | 1 · · · · · · · · · · · · · · · · · · ·                         |     |

| 7.5.2          | DPU electrical specification                                    |     |

| 7.5.2.1        |                                                                 |     |

| 7.5.2.2        | - · · · · · · · · · · · · · · · · · · ·                         |     |

| 7.5.3          | DPU power modes                                                 |     |

| 7.6            | Micro-interruption requirements                                 |     |

| 7.6.1          | PSE micro-interruption requirements                             |     |

| 7.6.2          | DPU micro-interruption specification                            | 58  |

| 8              | Power Splitter Characteristics                                  | 58  |

| 8.1            | General                                                         |     |

| 8.2            | Power Splitter class definition.                                |     |

| 8.3            | Description of Power Splitter Use Cases                         |     |

| 8.3.1          | General                                                         |     |

| 8.3.2          | DPU - case 1: No POTS service sharing the loop wiring           |     |

| 8.3.3          | DPU - case 2: With POTS service from the exchange               |     |

| 8.3.4          | DPU - case 3: With a Derived POTS service sharing the wiring    |     |

| 8.3.5          | CPE - case 1: No POTS service sharing the loop wiring           |     |

| 8.3.6          | CPE - case 2: With POTS service from the exchange               |     |

| 8.3.7          | CPE - case 3: With a derived POTS service sharing the wiring    |     |

| 8.4            | Power Splitter Requirements                                     |     |

| 8.4.1          | General                                                         |     |

| 8.4.2          | DSL Insertion Loss                                              | 65  |

| 8.4.3          | DSL Impedance Conversion                                        | 66  |

| 8.4.4          | DSL-Band Noise Attenuation                                      |     |

| 8.4.5          | DSL Port DC Isolation Resistance                                | 67  |

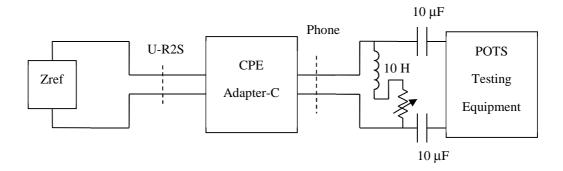

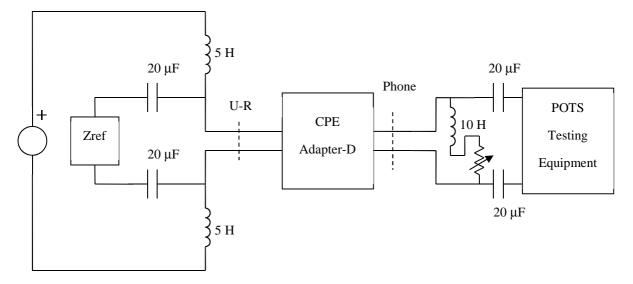

| 8.4.6          | POTS Measurement Procedure                                      | 67  |

| 8.4.7          | POTS Insertion Loss                                             | 68  |

| 8.4.8          | POTS Impedance Conversion                                       | 69  |

| 8.4.9          | POTS-band longitudinal Balance                                  | 70  |

| 8.4.10         | POTS-band Noise Attenuation                                     | 70  |

| 8.4.11         | POTS DC Isolation Resistance                                    | 70  |

| 8.4.12         | Tolerance to DC Feed                                            | 71  |

| 8.4.13         | Tolerance to Ringing                                            | 71  |

| 8.4.14         | Power Drain                                                     | 72  |

| 9              | POTS Adapter Characteristics                                    | 72  |

| 9.1            | Introduction                                                    |     |

| 9.1<br>9.2     | Description of POTS Adapters Use Cases                          |     |

| 9.2<br>9.2.1   | General                                                         |     |

| 9.2.1          |                                                                 |     |

| 9.2.2<br>9.2.3 | DPU - case 1: No POTS service sharing the loop wiring           |     |

| 9.2.3<br>9.2.4 | DPU - case 2: With a POTS service from the exchange - Adapter-E |     |

| 9.2.4<br>9.2.5 | DPU - case 3: With a derived POTS service sharing the wiring    |     |

| 9.2.5<br>9.2.6 | CPE - case 1: No POTS service snaring the loop wiring           |     |

| 9.2.6<br>9.2.7 | CPE - case 2: With a POTS service from the exchange - Adapter-C |     |

| 9.2.7<br>9.2.8 |                                                                 |     |

| 9.2.8<br>9.2.9 | CPE - case 3: With derived POTS sharing the wiring - Adapter-D  |     |

| 9.2.9<br>9.3   | CPE - case 3: With derived POTS sharing the wiring - Adapter-E  |     |

| 9.3<br>9.3.1   | POTS Adapter Requirements                                       |     |

| 9.3.1<br>9.3.2 | DSL Insertion Loss                                              |     |

| 9.3.2<br>9.3.3 | DSL Insertion Loss                                              |     |

| 7))            | DSD IIIDEGAICE COILVEISIOII                                     | / ð |

| 9.3.4<br>9.3.5 |                      | e Generation                                     |     |

|----------------|----------------------|--------------------------------------------------|-----|

| 9.3.5<br>9.3.6 |                      | Loss                                             |     |

| 9.3.0<br>9.3.7 |                      | ce Conversion                                    |     |

| 9.3.7<br>9.3.8 |                      | gitudinal Balance                                |     |

| 9.3.9          | •                    | nnel Noise                                       |     |

| 9.3.1          | 2 2                  | tion Resistance                                  |     |

| 9.3.1          |                      | on                                               |     |

| 9.3.1          | 2 2                  | tion                                             |     |

| 9.3.1          |                      | tion                                             |     |

| 9.3.1          | 4 DC Feed Genera     | ation                                            | 86  |

| 9.3.1          |                      |                                                  | 87  |

| 9.3.1          |                      | ection                                           |     |

| 9.3.1          |                      |                                                  |     |

| 9.3.1          |                      |                                                  |     |

| Ann            |                      | Reverse power backup systems                     |     |

| A.1            |                      | p in the CPE                                     |     |

| A.2            | Case 2 battery backu | p in the DPU and CPE                             | 89  |

| Ann            | ex B (normative):    | General POTS requirements                        | 90  |

| Ann            | ex C (informative):  | RPF Noise Limits For Common Mode                 | 91  |

| C.1            | Introduction         |                                                  | 91  |

| C.2            | Derivation           |                                                  | 91  |

| C.3            | Cable Balance Mode   | el and Common Mode PSD Construction              | 91  |

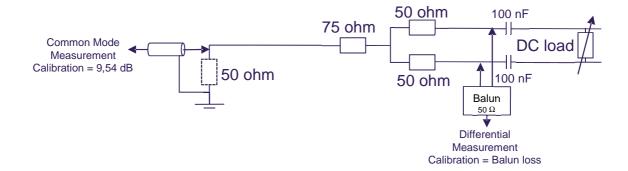

| C.4            | Example of Measure   | ment Environment                                 | 91  |

| Ann            | ex D (informative):  | Out-of-Band Signalling Channel for POTS Adapters | 93  |

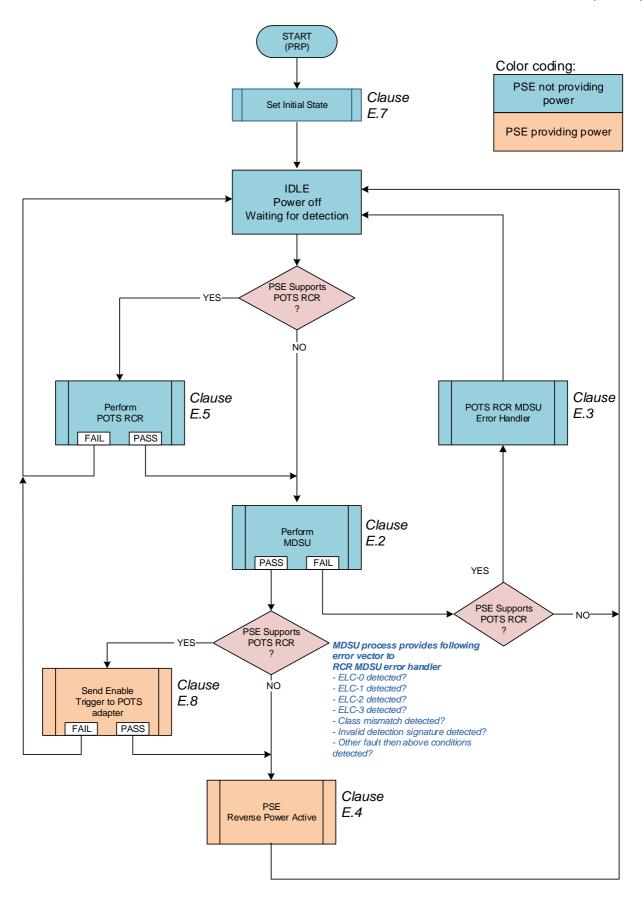

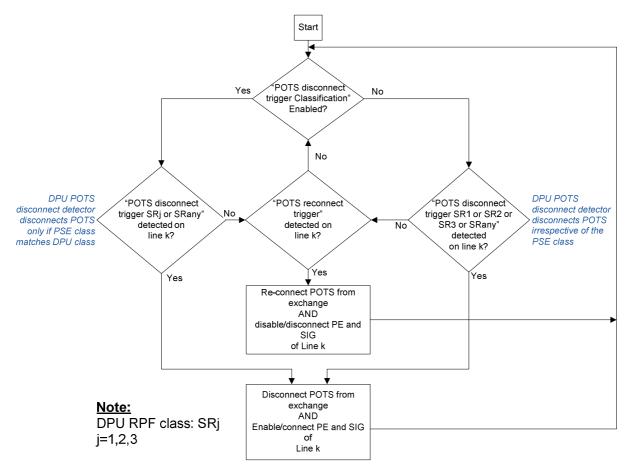

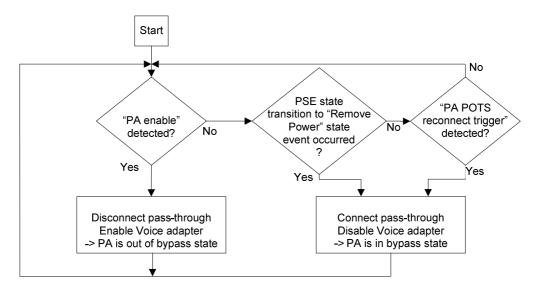

| Ann            | ex E (normative):    | PRP PSE low level flow charts                    |     |

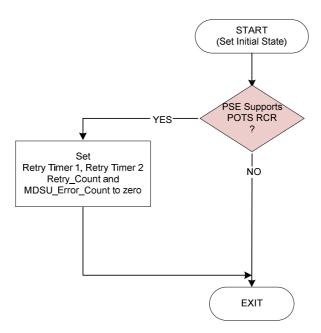

| E.1            |                      |                                                  |     |

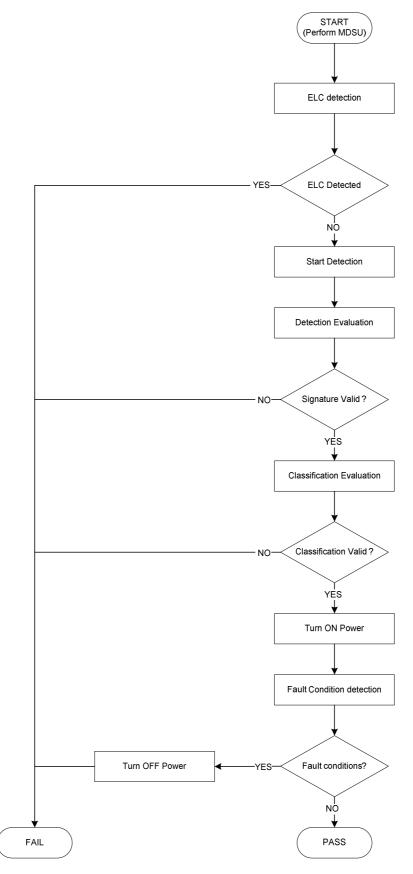

| E.2            | Perform MDSU         |                                                  | 96  |

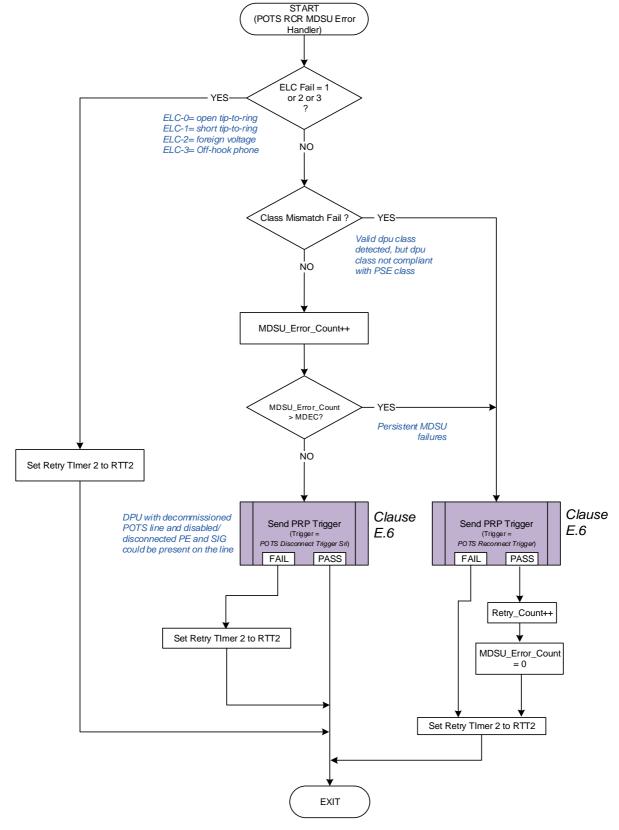

| E.3            | POTS RCR MDSU I      | Error Handler                                    | 97  |

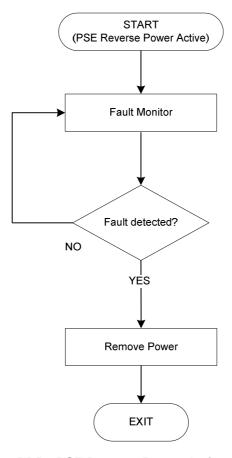

| E.4            | PSE Reverse Power    | Active                                           | 98  |

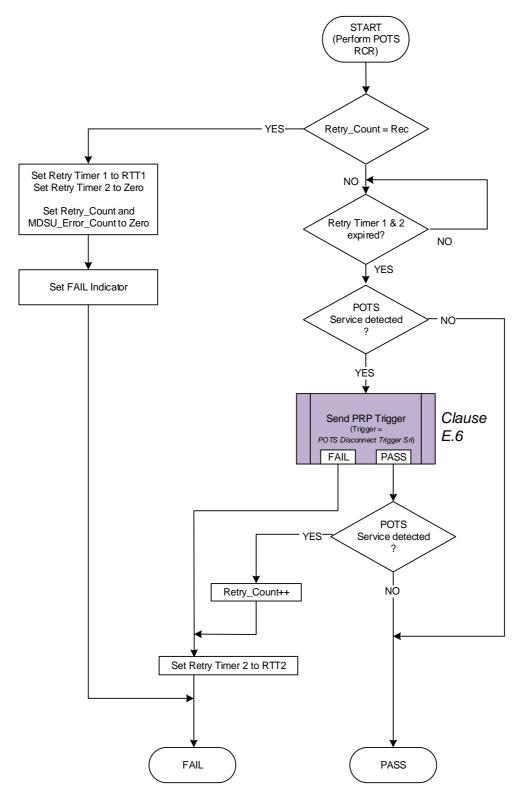

| E.5            | Perform POTS RCR     |                                                  | 99  |

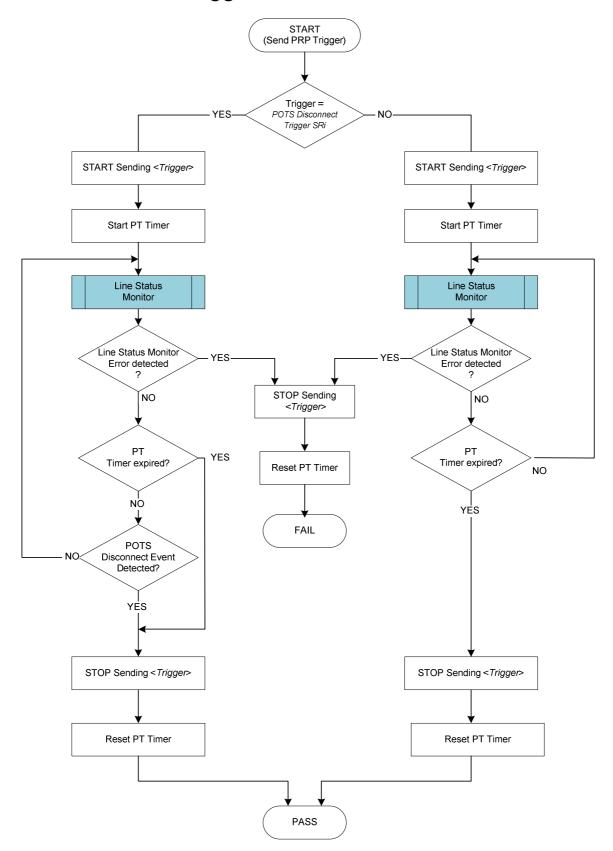

| E.6            |                      |                                                  |     |

| E.7            | 22                   |                                                  |     |

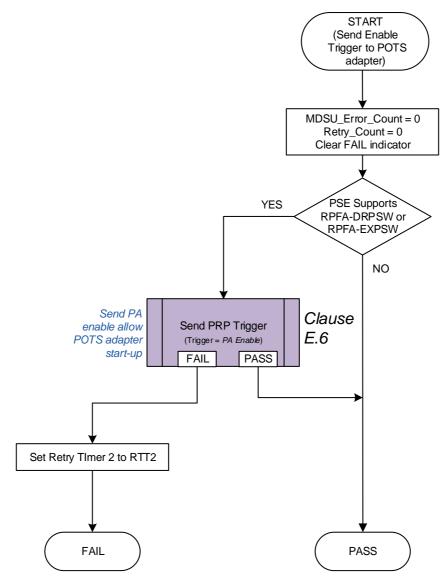

| E.8            |                      | to POTS Adapter                                  |     |

|                | ex F (informative):  | Long Range RPF Classification                    |     |

|                | ,                    |                                                  |     |

|                | ex G (informative):  | Bibliography                                     |     |

|                | ex H (informative):  | Change History                                   |     |

| Lieta          |                      |                                                  | 106 |

# Intellectual Property Rights

#### **Essential patents**

IPRs essential or potentially essential to normative deliverables may have been declared to ETSI. The information pertaining to these essential IPRs, if any, is publicly available for **ETSI members and non-members**, and can be found in ETSI SR 000 314: "Intellectual Property Rights (IPRs); Essential, or potentially Essential, IPRs notified to ETSI in respect of ETSI standards", which is available from the ETSI Secretariat. Latest updates are available on the ETSI Web server (https://ipr.etsi.org/).

Pursuant to the ETSI IPR Policy, no investigation, including IPR searches, has been carried out by ETSI. No guarantee can be given as to the existence of other IPRs not referenced in ETSI SR 000 314 (or the updates on the ETSI Web server) which are, or may be, or may become, essential to the present document.

#### **Trademarks**

The present document may include trademarks and/or tradenames which are asserted and/or registered by their owners. ETSI claims no ownership of these except for any which are indicated as being the property of ETSI, and conveys no right to use or reproduce any trademark and/or tradename. Mention of those trademarks in the present document does not constitute an endorsement by ETSI of products, services or organizations associated with those trademarks.

#### **Foreword**

This Technical Specification (TS) has been produced by ETSI Technical Committee Access, Terminals, Transmission and Multiplexing (ATTM).

The present document is part 1 of a multi-part deliverable covering the European requirements for reverse powering of remote access equipment, as identified below:

Part 1: "Twisted pair networks";

Part 2: "Coaxial cable networks".

# Modal verbs terminology

In the present document "shall", "shall not", "should", "should not", "may", "need not", "will", "will not", "can" and "cannot" are to be interpreted as described in clause 3.2 of the <u>ETSI Drafting Rules</u> (Verbal forms for the expression of provisions).

"must" and "must not" are NOT allowed in ETSI deliverables except when used in direct citation.

### Introduction

As various Operators consider the deployment of fibre-fed remote nodes that contain xDSL DSLAM equipment, it is necessary to consider the means of powering such remotely located equipment. One such method, known as "reverse power feed", transmits the power from the customer premises to the fibre-fed remote node using the distribution-side copper network. The present document defines a reverse power feed transmission standard which allows Operators to source suitably compliant equipment for inclusion in their networks. The reverse power feed methodology can be used to power a remote node hosting any metallic transmission system (e.g. G.fast [i.4], VDSL2 [i.3], etc.).

# 1 Scope

The present document defines architectures and specifications for reverse powering of remote network nodes from one or multiple CPEs over twisted pair networks. The architectures describe how to combine reverse power feed with the data only, VoIP and POTS line services. Start-up protocols are defined to ensure proper interaction between the line services and the reverse power system. Operations and maintenance requirements for managing the reverse power feed and power combining within the remote network node are specified. The present document also identifies power splitter and POTS Adapter requirements.

### 2 References

#### 2.1 Normative references

References are either specific (identified by date of publication and/or edition number or version number) or non-specific. For specific references, only the cited version applies. For non-specific references, the latest version of the referenced document (including any amendments) applies.

Referenced documents which are not found to be publicly available in the expected location might be found at <a href="https://docbox.etsi.org/Reference/">https://docbox.etsi.org/Reference/</a>.

NOTE: While any hyperlinks included in this clause were valid at the time of publication, ETSI cannot guarantee their long term validity.

The following referenced documents are necessary for the application of the present document.

Part 1: Safety requirements".

| [1] | ETSI ES 202 971: "Access and Terminals (AT); Public Switched Telephone Network (PSTN); Harmonized specification of physical and electrical characteristics of a 2-wire analogue interface for short line interface".                                                                                              |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [2] | CENELEC EN 60950-1: "Information Technology Equipment - Safety - Part 1: General requirements (IEC 60950-1:2005 + Cor.:2006 + A1:2009, modified)".                                                                                                                                                                |

| [3] | ETSI ES 203 021: "Access and Terminals (AT); Harmonized basic attachment requirements for Terminals for connection to analogue interfaces of the Telephone Networks; Update of the technical contents of TBR 021, EN 301 437, TBR 015, TBR 017".                                                                  |

| [4] | Broadband Forum TR-301: "Architecture and Requirements for Fiber to the Distribution Point", Issue 1.                                                                                                                                                                                                             |

| [5] | Broadband Forum TR-286: "Testing of Metallic Line Testing (MELT) functionality on xDSL Ports".                                                                                                                                                                                                                    |

| [6] | IEC 61000-4-11: "Electromagnetic compatibility (EMC) - Part 4-11: Testing and measuring techniques - Voltage dips, short interruptions and voltage variations immunity tests".                                                                                                                                    |

| [7] | ETSI TS 101 952-1: "Access network xDSL splitters for European deployment; Part 1: Generic specification of xDSL over POTS splitters".                                                                                                                                                                            |

| [8] | ETSI ES 203 021-3: "Access and Terminals (AT); Harmonized basic attachment requirements for Terminals for connection to analogue interfaces of the Telephone Networks; Update of the technical contents of TBR 021, EN 301 437, TBR 015, TBR 017; Part 3: Basic Interworking with the Public Telephone Networks". |

| [9] | CENELEC EN 62368-1: "Audio/video, information and communication technology equipment -                                                                                                                                                                                                                            |

#### 2.2 Informative references

References are either specific (identified by date of publication and/or edition number or version number) or non-specific. For specific references, only the cited version applies. For non-specific references, the latest version of the referenced document (including any amendments) applies.

NOTE: While any hyperlinks included in this clause were valid at the time of publication, ETSI cannot guarantee their long term validity.

The following referenced documents are not necessary for the application of the present document but they assist the user with regard to a particular subject area.

| •       | •                                                                                                                                                                                                                                           |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [i.1]   | Void.                                                                                                                                                                                                                                       |

| [i.2]   | NICC ND 1645 (V1.1.2) (2011-06): "NGA Telephony; Architecture and requirements".                                                                                                                                                            |

| NOTE: A | vailable at <a href="https://niccstandards.org.uk/wp-content/uploads/2019/03/ND1645v1.1.2.pdf">https://niccstandards.org.uk/wp-content/uploads/2019/03/ND1645v1.1.2.pdf</a> .                                                               |

| [i.3]   | Recommendation ITU-T G.993.2: "Very high speed digital subscriber line transceivers 2 (VDSL2)".                                                                                                                                             |

| [i.4]   | Recommendation ITU-T G.9700: "Fast access to subscriber terminals (G.fast) - Power spectral density specification".                                                                                                                         |

| [i.5]   | Recommendation ITU-T G.9701: "Fast access to subscriber terminals (G.fast) - Physical layer specification".                                                                                                                                 |

| [i.6]   | ETSI TS 101 271 (V1.2.1): "Access, Terminals, Transmission and Multiplexing (ATTM); Access transmission systems on metallic access cables; Very High Speed digital subscriber line system (VDSL2) [Recommendation ITU-T G.993.2 modified]". |

| [i.7]   | Recommendation ITU-T G.998.4, Annex E: "Low Power Mode operation with ITU-T G.993.2 and G.993.5".                                                                                                                                           |

| [i.8]   | Recommendation ITU-T G.9701, Amendment 1 (2014): "Support of Low power operation and all functionality necessary to allow transceivers to be deployed as part of reverse powered (and possibly battery operated) network equipment".        |

|         |                                                                                                                                                                                                                                             |

Recommendation ITU-T G.992.5: "Asymmetric digital subscriber line 2 transceivers (ADSL2)

# 3 Definition of terms, symbols and abbreviations

Extended bandwidth ADSL2 (ADSL2plus)".

#### 3.1 Terms

[i.9]

For the purposes of the present document, the following terms apply:

**broadband bypass:** scenario whereby the DPU supports "Reverse Power Feed Architecture - No POTS with Broadband Bypass" (RPFA NOP-BB) as defined in clause 5.8

NOTE: The scenario whereby the DPU supports ZT-RCR defined in clause 7.4 whereby exchange POTS is not present on the line, but where there is an overlay DSL service (i.e. "naked" or "dry" DSL).

**bypass mode:** operational state of the POTS adapters or power splitter where there is a metallic connection to the exchange or to an ATA

NOTE: This also refers to the operational state of the stateless Switching Function (SF) specifically for the RPFA-NOPBB architecture option, where the xTU-R of the CPE is connected to the xTU-O of the CO/cabinet.

**metallic connection:** physical connectivity providing a DC path between two points, typically provided via a pair of twisted copper (or aluminium) wires

**normal mode:** operational state of the POTS adapters or power splitter where there is no metallic connection to the exchange or to an ATA

NOTE: This also refers to the operational state of the stateless Switching Function (SF), specifically for the RPFA-NOPBB architecture option, where the xTU-R of the CPE is connected to the xTU-O of the DPU.

**normal operation:** state of a system (i.e. a DPU reversely powered by a PSE) reached after the start-up procedure has been completed

**POTS adapter:** device that provides DC isolation between reverse power feed and POTS DC feed to allow a POTS service to share the same wires as those used by reverse power feed

POTS DC feed: DC current presented at a POTS adapter to power a plain old telephone

**POTS Remote Copper Reconfiguration (RCR):** scenario where POTS from the exchange may be provided to the subscriber and shall be disconnected by the DPU, prior to start-up of the DPU

**power splitter:** device that performs a frequency splitting/combining function between the AC part of the services being carried (which can include POTS and xDSL based services) and the injected DC electrical power

NOTE: The power splitter does not include a DC-blocking high-pass function.

RING: other leg of a twisted pair

service splitter: low pass filter that separates baseband POTS from xDSL frequencies

NOTE: The relevant specifications for the service splitter can be found in ETSI TS 101 952-1 [7].

**start-up mode:** start-up procedure of a system (powering part of a DPU and PSE)

**TIP:** one leg of a twisted pair

#### 3.2 Symbols

For the purposes of the present document, the following symbols apply:

| Ω     | Ohm                                                                                   |

|-------|---------------------------------------------------------------------------------------|

| μF    | micro Farad                                                                           |

| nF    | nano Farad                                                                            |

| R     | 2-wire analogue presented interface                                                   |

| U-R   | Reference point at CPE containing both DC power and service data                      |

| U-R2  | Reference point at CPE containing the filtered service data                           |

| U-R2P | Reference point at CPE containing the injected DC power                               |

| U-R2S | Reference point at CPE containing the baseband POTS and the converted POTS signalling |

| U-O   | Reference point at DPU containing both DC power and service data                      |

| U-O2  | Reference point at DPU containing the filtered service data                           |

| U-O2O | Reference point at DPU containing the baseband POTS and the converted POTS signalling |

| U-O2P | Reference point at DPU containing the extracted DC power                              |

#### 3.3 Abbreviations

For the purposes of the present document, the following abbreviations apply:

| AC     | Alternating Current                |

|--------|------------------------------------|

| ACM    | Alternating Current Mains          |

| ADSL   | Asymmetric Digital Subscriber Line |

| ATA    | Analogue Telephone Adapter         |

| BAT    | Battery                            |

| BBA    | Battery Back-up Available          |

| CO     | Central Office                     |

| CP     | Customer Premises                  |

| CPE    | Customer Premises Equipment        |

| CPE ME | CPE's Management Entity            |

CPF Common Power Feed

DC Direct Current

DGL Dying Gasp Loss

DN Distribution Network

DP Distribution Point

DPU Distribution Point Unit

DPU ME DPU's Management Entity

DR Diode/Resistor

DSL Digital Subscriber Line

DSLAM Digital Subscriber Line Access Multiplexer

ELC Error Line Condition

EXPSW Exchange Sharing the in-premises Wiring

FSK Frequency Shift Keying

FTTdp Fibre To The distribution point

FTU G.fast Transceiver Unit

NOTE: See Recommendation ITU-T G.9701 [i.5].

FTU-O FTU at the DPU

FTU-R FTU at the remote site

HON Higher Order Node

IFN Intensity of current Feed Now

LPF Low Pass Filter

LR Long Range

LSU Last Start Up

MDSU Metallic Detection based Start-Up protocol

ME Management Entity

MELT Metallic Loop Test

NMS Network Management System

NT Network Termination

NTE Network Termination Equipment OAM Operations And Maintenance

OHP Off-Hook Phone

PC Power Class

PE Power Extractor

PHY Physical (layer)

PMA Persistent Management Agent

PME-C CPE's Power Management Entity

PME-D DPU's Power Management Entity

PMT Power Management Transceiver

POTS Plain Old Telephony Service

PRP POTS Remote Copper Reconfiguration (RCR) Protocol

PS Power Splitter

PSD Power Spectral Density PSE Power Source Equipment

PSU Power Supply Unit (including the combiner function if multiple lines are active)

PT PRP Trigger

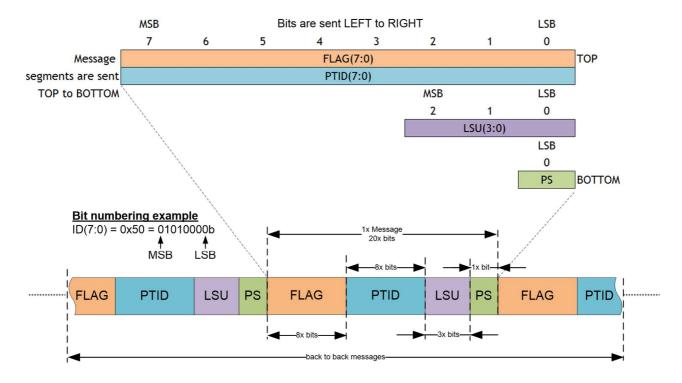

PTID PRP Trigger IDentification RBW Resolution Bandwidth RC Resistor/Capacitor

RCR Remote Copper Reconfiguration RPCE Reverse Power Control Entity

RPF Reverse Power Feed

RPFA Reverse Power Feed Architecture

RPFA-DRP Reverse Power Feed Architecture - DeRived POTS

RPFA-DRPSW Reverse Power Feed Architecture - DeRived POTS Sharing in-Premises Wiring

RPFA-EXP Reverse Power Feed Architecture - EXchange POTS

RPFA-EXPSW Reverse Power Feed Architecture - EXchange POTS Sharing in-Premises Wiring

RPFA-NOP Reverse Power Feed Architecture - No POTS

RPFA-NOPBB Reverse Power Feed Architecture - No POTS with Broadband Bypass

$\begin{array}{ll} R_{SIG} & Signature \ Resistor \\ SCF & Switch \ Control \ Function \end{array}$

| SF    | Switching Function                      |

|-------|-----------------------------------------|

| SG    | Service Gateway                         |

| SIG   | SIGnature                               |

| SR    | Short Range                             |

| SS    | Service Splitter                        |

| TNV   | Telecommunication Network Voltage       |

| UPS   | Uninterrupted Power Supply              |

| VA    | Volt Ampere                             |

| VDSL  | Very high speed Digital Subscriber Line |

| VoIP  | Voice over Internet Protocol            |

| VPSE  | steady state Voltage from PSE           |

| xDSL  | unspecified DSL variant                 |

| xTU-O | FTU-O or VTU-O                          |

| xTU-R | FTU-R or VTU-R                          |

Zener/Resistor/Capacitor **ZT-LAC** Zero Touch Link Auto Configuration **ZT-RCR** Zero Touch Remote Copper Reconfiguration

**ZRC**

#### 4 Introduction to Reverse Power Feed

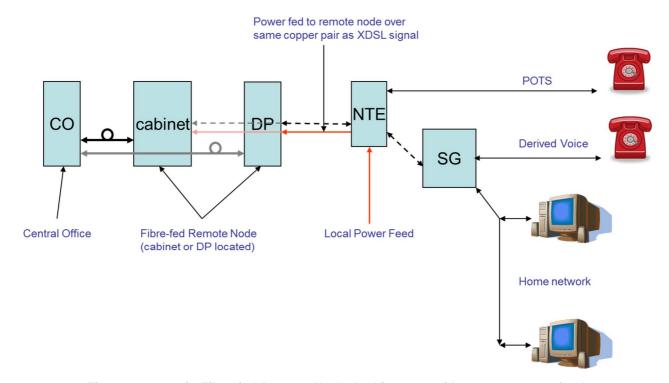

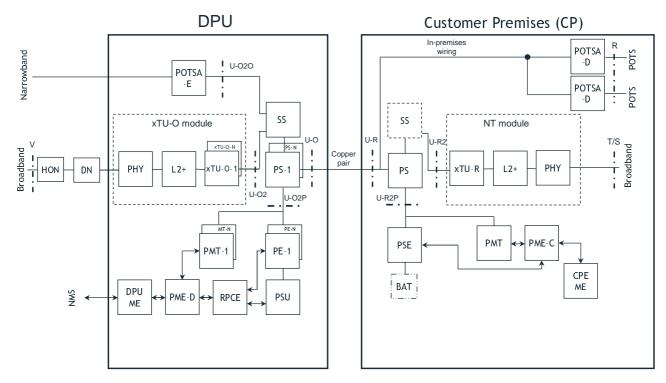

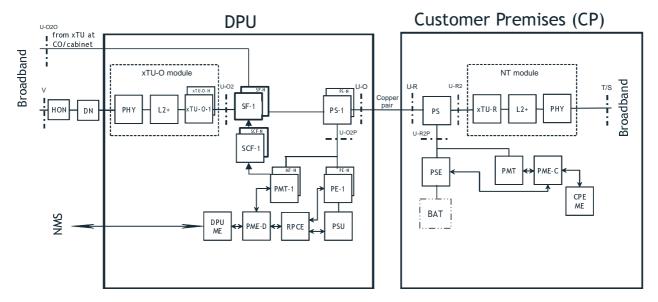

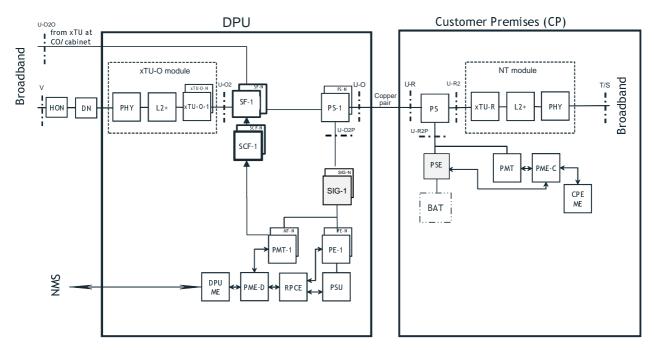

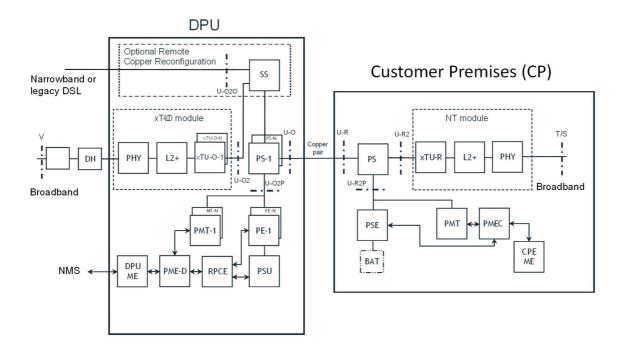

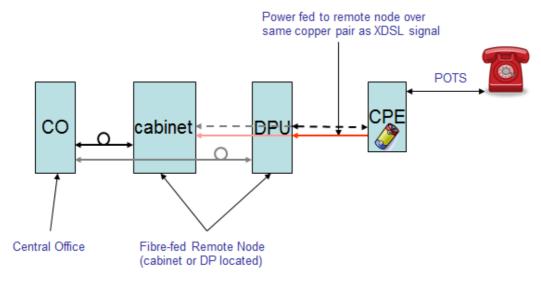

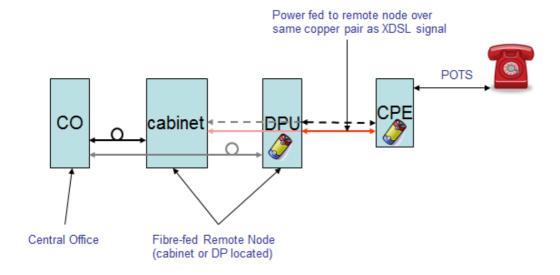

The basic architecture of a fibre-fed remote node with reverse power feed is shown in Figure 1.

Figure 1: Generic Fibre-fed Remote Node Architecture with reverse power feed

Figure 1 shows power being injected at the NTE from a local power source (located within the home and/or building) which traverses the local loop to power a fibre-fed remote node which can be located at either the Distribution Point (DP) or street cabinet using the same copper pair cable that is used to transmit the xDSL to/from the home/fibre-fed remote node. A metallic POTS service is shown at the NTE. Voice services can also be implemented as a derived service from the Service Gateway (SG).

An issue with regards to reverse powered fibre-fed nodes is that of who or what is responsible for the powering of common circuitry contained within the node. It is easy to envisage that an individual user should be responsible for the powering of the remote line terminating/driver electronics corresponding to his particular circuit. However, it is not so easy to determine who or what is responsible for powering of say the DPU that terminates the fibre link.

There may be occasions where only a single user is providing power to the remote node but this may not be sufficient to power all of the remote node electronics for proper operation.

It is recognized that one single (i.e. generic) specification cannot consider all possible architectural variants, therefore the present document has been organized as a series of architecture options and equipment shall adhere to one or more of these options.

In the present document, two different implementations of Power Source Equipment (PSE) for Customer Premises are considered: standalone (i.e. a two box model where the PSE and NTE are separate) or integrated (i.e. a single box model where the PSE and NTE are integrated). In these implementations, the Power Splitter (PS) may either be integrated or stand alone.

### 5 Reverse Power Feed Architecture

#### 5.1 Basics of RPF

Reverse power feed is one of three DPU powering methods defined in TR-301 [4]. Here, the DPU draws its power from the customer premises via the copper lines between those premises and the DPU. The reverse power feed capacity and DPU power consumption need to be such that the DPU can be fully operational when only a single customer is connected. Any back-up battery would be located in the customer premises.

The other two methods are:

- Forward Power from a Network Power Node. In this case, any back-up battery would be located at the network power node.

- Local Power from AC mains source. In this case, any back-up battery would be located at the DPU location.

The combination of reverse powering with one or both of the other two methods is outside the scope of the present document.

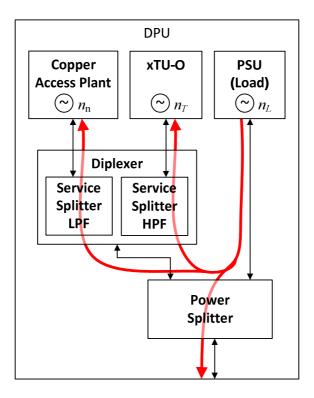

Reverse powering shall have two power splitters (one located at the customer premises and another at the remote node) to enable power to be inserted at the customer end of a link and extracted at the remote node. Each power splitter performs a frequency splitting and combining function between the services being carried (which can include POTS and xDSL based services) and the injected DC electrical power.

Within the remote node, if it operates with multiple power-fed lines then there shall be a power extraction and combiner unit. The purpose of this unit is to combine the multiple power feed inputs to produce a single power source output. The power load should be shared amongst the input power sources.

The technical specifications in the present document shall apply to each architecture described below as one of the six options shown in Table 1. The optional reverse power battery backup at the customer premises is illustrated in block BAT for each reference model.

| Option | Name       | Description                                                                |  |  |

|--------|------------|----------------------------------------------------------------------------|--|--|

| 1      | RPFA-NOP   | Reverse Power Feed Architecture - No POTS                                  |  |  |

| 2      | RPFA-EXP   | Reverse Power Feed Architecture - Exchange POTS                            |  |  |

| 3      | RPFA-EXPSW | Reverse Power Feed Architecture - Exchange POTS Sharing in-premises Wiring |  |  |

| 4      | RPFA-DRP   | Reverse Power Feed Architecture - Derived POTS                             |  |  |

| 5      | RPFA-DRPSW | Reverse Power Feed Architecture - Derived POTS Sharing in-premises Wiring  |  |  |

| 6      | RPFA-NOPBB | Reverse Power Feed Architecture - No POTS with Broadband Bypass            |  |  |

**Table 1: Architecture Options for Reverse Power Feed**

#### 5.2 Reverse Power Feed and POTS Co-Existence

#### 5.2.1 Overview

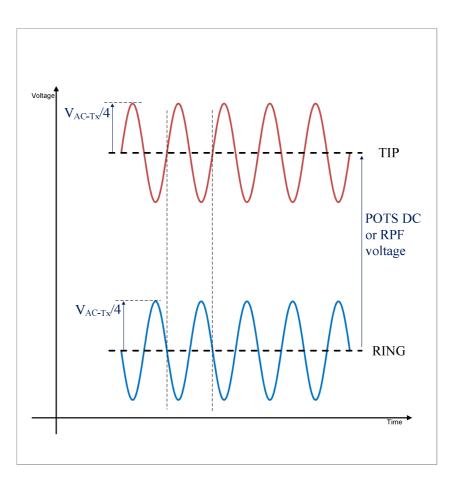

Table 1, option 2 to option 5 involve reverse power feed co-existing with POTS - whether this is exchange based POTS (RPFA-EXP, RPFA-EXPSW) or derived POTS (RPFA-DRP, RPFA-DRPSW).

When a POTS service is present on the same wire pair as reverse power feed (option 2, option 3 and option 5) the POTS DC feed will be removed and the DC signalling/low frequency signalling will be translated so that it uses another part of the baseband spectrum, but the basic analogue voice signal remains essentially untouched. At the CP, DC feed and the signalling are restored and POTS is presented as normal.

When POTS is provided by derived voice service (option 4 and option 5), low power (L2) modes [i.7] and [i.8] may be used to provide the voice service even when the entire payload is not required by other services.

In order to achieve co-existence between reverse power feed and POTS, various adapters are required as described in clause 5.2.2 for use in the reverse power feed reference models.

#### 5.2.2 POTS Adapters

#### 5.2.2.1 General

The following three different types of POTS Adapter are specified for use in the reverse power feed reference models:

- 1) POTS Adapter E (POTSA-E).

- 2) POTS Adapter C (POTSA-C).

- 3) POTS Adapter D (POTSA-D).

Where reverse power feed and POTS signals traverse the same copper wires, a signalling system shall be implemented to allow the signalling at the POTS interface based on off-hook/on-hook DC impedance, presence/absence of ringing signal, and in those jurisdictions requiring it, line reversal for Calling Number ID alerting to be communicated across the copper pair from the DPU to the POTS terminals. This functionality can be provided by the various POTS Adapters described in clauses 5.2.2.2, 5.2.2.3 and 5.2.2.4.

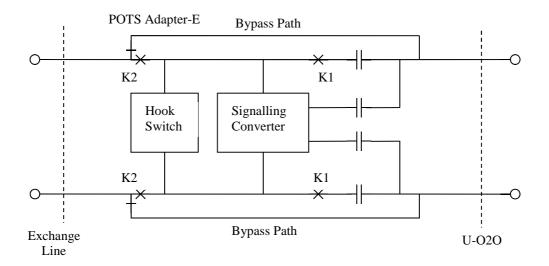

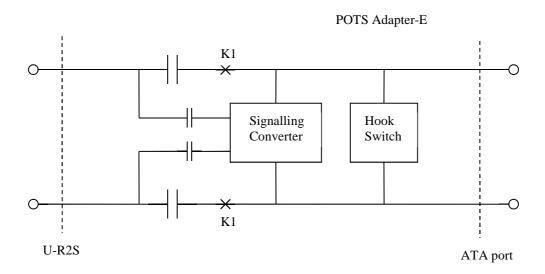

#### 5.2.2.2 POTS Adapter - E (POTSA-E)

POTS Adapter - E is the single adapter located at the DPU and this adapter shall perform the following functions:

- 1) Translate the downstream DC feed and low frequency POTS signalling into an in-band or out-of-band signalling system.

- 2) Translate the signals from the upstream in-band or out-of-band signalling system into DC and low frequency POTS signalling.

POTSA-E may provide a relay by-pass when un-powered (for life-line operation) or when signalled to provide direct access to the exchange to allow operations such as line-test to be performed.

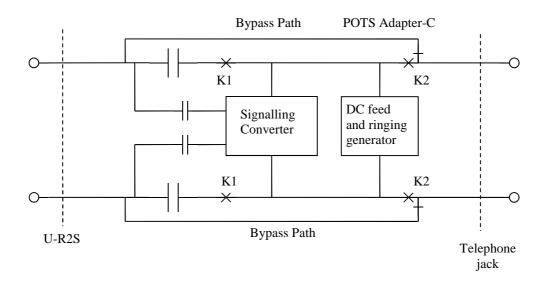

#### 5.2.2.3 POTS Adapter - C (POTSA-C)

POTS Adapter - C is the single adapter located at the NT module and this adapter shall perform the following functions:

- 1) Translate the upstream DC and low frequency POTS signalling from the POTS Terminal into an in-band or out-of-band signalling system.

- Translate the downstream in-band or out-of-band signalling system into POTS signalling towards the POTS Terminal.

- 3) Restore the downstream DC feed while providing sufficient current limit and DC voltage to supply one or more phone devices.

4) Provide a pre-defined rate of change of current increase when a phone device goes off-hook to allow for the detection of phone devices going off-hook that do not have the correct POTS Adapter fitted.

POTSA-C may provide relay by-pass when un-powered (for lifeline operation) or when signalled to provide direct access to the exchange to allow operations such as line-test to be performed.

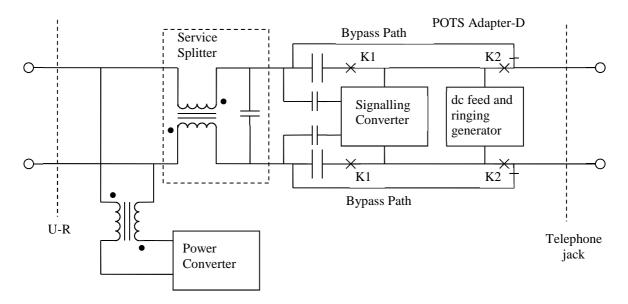

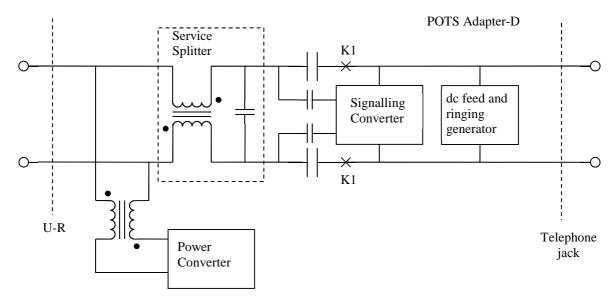

#### 5.2.2.4 POTS Adapter - D (POTSA-D)

POTS Adapter - D is the adapter that can be attached to every phone device connected to the in-premises wiring on the home network. This adapter operates in the presence of reverse powering. This adapter shall perform the following functions:

- 1) Translate the signals from the upstream DC and low frequency POTS signalling from the POTS Terminal into an in-band or out-of-band signalling system.

- 2) Translate the signals from the downstream in-band or out-of-band signalling system into POTS signalling towards the POTS Terminal.

- 3) Restore the downstream DC feed while providing sufficient current limit and DC voltage to supply a single phone device.

- 4) Provide a pre-defined rate of change of current increase when a phone device goes off-hook to allow for the detection of phone devices going off-hook that do not have the correct POTS Adapter fitted.

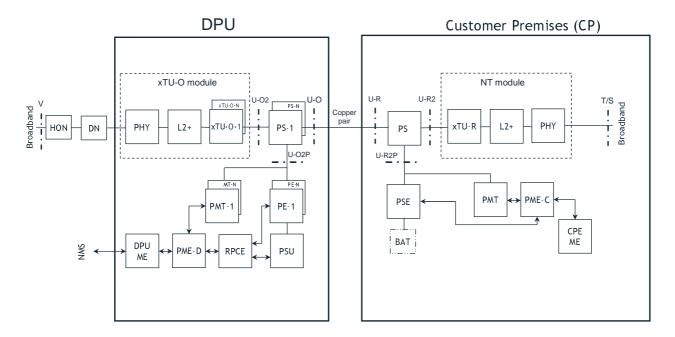

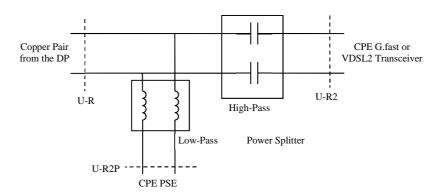

# 5.3 Reverse Power Feed Architecture without POTS on the same pair (RPFA-NOP)

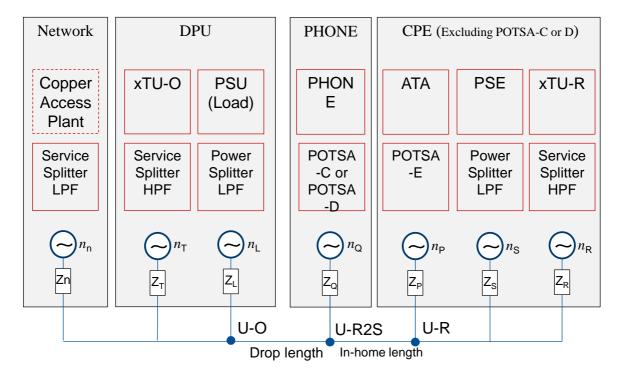

The functional reference model of the reverse power feed architecture without POTS on the same pair (RPFA-NOP) is shown in Figure 2 and the associated reference points are detailed in Table 2. In this option, the reference model illustrates the RPF architecture with the broadband service only and no underlying narrowband service, neither exchange-based POTS nor derived POTS.

The xTU-O is located inside the Distribution Point Unit (DPU) at the network side of the wire pair (U-O reference point). The xTU-R is located inside the Network Termination (NT) at the customer premises side of the wire pair (U-R reference point). Each DPU is located at a distribution point and can contain one or more xTU-O transceivers (xTU-O-I, I = 1...N), with each transceiver connected to a NT.

At the backhaul link termination, the PHY blocks represent the physical layer of the xTU-O module towards the access network and of the NT towards the Customer Premises (CP). These blocks are shown for completeness of the data flow but are out of scope of the present document. The L2+ blocks represent the Layer 2 and above functionalities contained in the xTU-O module and the NT. These blocks are shown for completeness of the data flow but are out of scope of the present document.

The traffic from all DPUs is aggregated by a backhaul transmission system operating over the Distribution Network (DN) and Higher Order Node (HON) up to the V reference point. The type of transmission system is out of scope of the present document.

The management of a DPU is performed by the Network Management System (NMS), passing management information to the DPU's Management Entity (DPU ME) over a management communications channel that is provided over the backhaul transmission system. The details of the management communications channel and most of the management functionality required for the DPU are out of scope of the present document.

As there is a need for management transactions between the DPU and the CPE for controlling the start-up of reverse powering to the DPU when mains power is applied to the CPE and for monitoring powering in normal operations, Power Management Transceivers (PMT) are connected to the copper drop in the DPU (PMT-I, I = 1...N) and the customer premises to support a management protocol. The management information is exchanged between the PMT-I and DPU ME through the power management entity PME-D. At the customer premises, the information flow takes place between the PMT and CPE ME through the power management entity PME-C.

The power is inserted on the line (i.e. copper pair) by the Power Source Equipment (PSE) located in the customer premises and extracted from the line by the Power Extractor (PE-I, I = 1...N) located in the DPU. Power is extracted from each active port and combined in the Power Supply Unit (PSU) and coordinated over all lines by the Reverse Power Control Entity (RPCE). The PE and PSU are separated from the broadband signal on the line (at reference point U-O and U-R) by a Power Splitter (PS).

Figure 2: RPFA-NOP Reference Model

Out of band POTS **Reference Point Broadband Signals Reverse Power Analogue Voice** Feeding Signals Signalling U-O2 Yes Yes No No U-O2P No Yes No No U-O/U-R Yes No No Yes U-R2P No Yes No No U-R2 Yes No No

**Table 2: RPFA-NOP Reference Points**

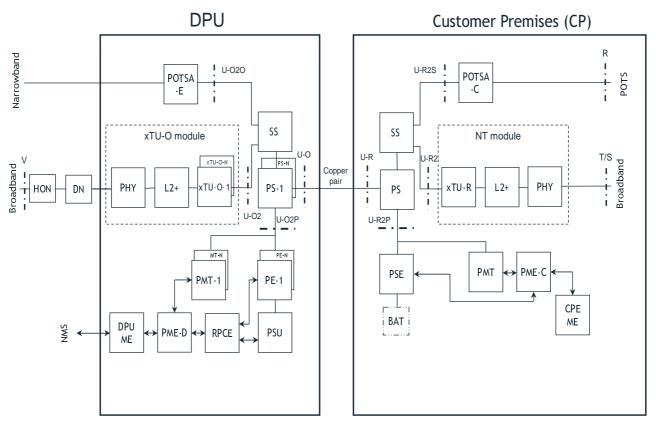

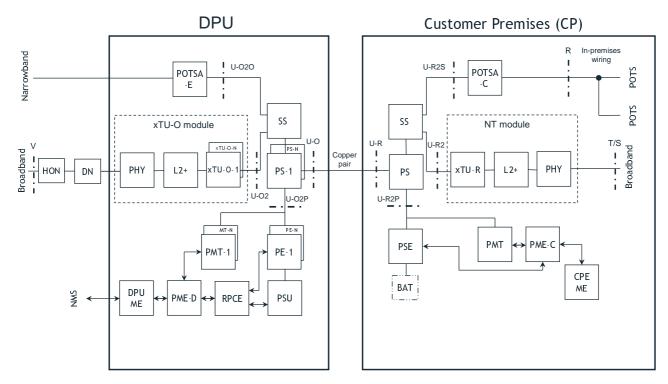

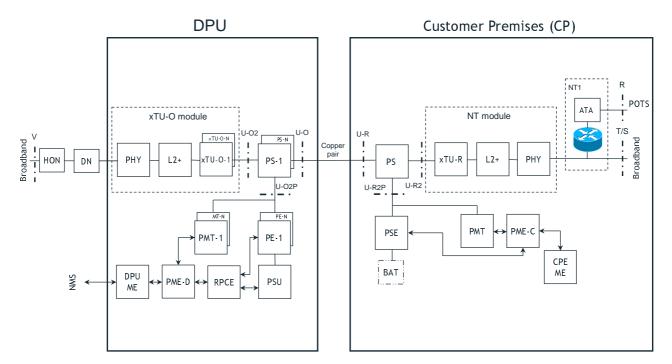

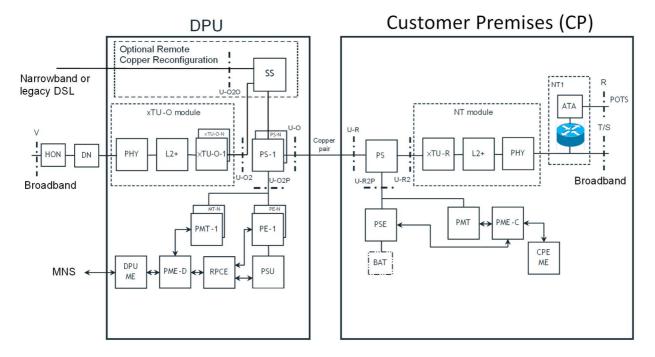

# 5.4 Reverse Power Feed Architecture with Baseband POTS from the Exchange (RPFA-EXP)

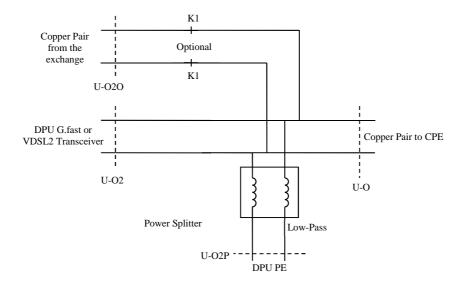

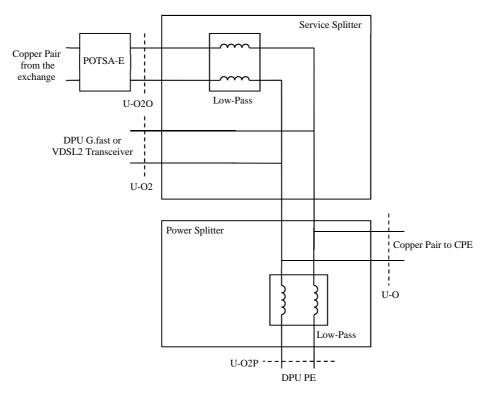

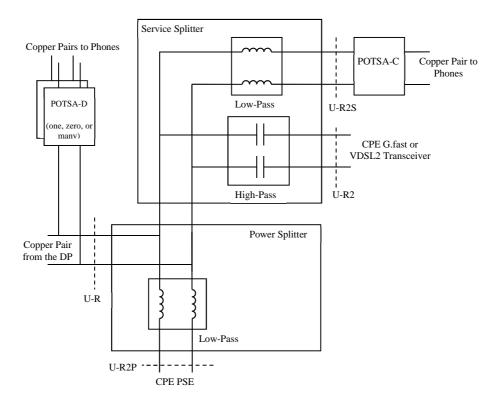

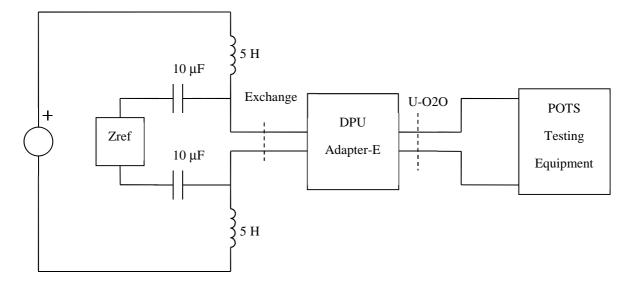

The functional reference model of the reverse power feed architecture with baseband POTS from the exchange (RPFA-EXP) is shown in Figure 3 and Figure 4 and the associated reference points are detailed in Table 3.

This option includes two different variants. Figure 3 illustrates the case where a dedicated POTS port is used to connect a single POTS device while the remaining customer premises equipment CPE (Power Splitter (PS), Service Splitter (SS), Power Source Equipment (PSE) and NT module) may be located anywhere on the in-premises wiring. The single POTS Adapter (POTSA-C) is also located at the same place as the rest of the CPE.

The second variant shown in Figure 4, illustrates the case where the CPE (Power Splitter (PS), Service Splitter (SS), Power Source Equipment (PSE) and NT module) and the POTSA-C adapter are installed at the master-socket location while multiple POTS devices are connected to the existing in-premises wiring.

In both cases it is expected that baseband voice is transmitted between the DPU and the customer premises and the function of the POTS Adapter in the DPU (POTSA-E) and POTS Adapter in the customer premises (POTSA-C) is concerned with the POTS signalling translation. Also in both cases, there is no requirement for an individual POTSA-D to be attached to each individual phone device within the customer premises.

Figure 3: RPFA-EXP Reference Model

Figure 4: RPFA-EXP Reference Model with multiple POTS distributed over In-Premises Wiring

**Table 3: RPFA-EXP Reference Points**

| Reference Point | Broadband Signals | Reverse Power<br>Feed | Analog Voice<br>Signals | Out of band POTS<br>Signalling |

|-----------------|-------------------|-----------------------|-------------------------|--------------------------------|

| U-O2            | Yes               | Yes                   | No                      | No                             |

| U-O2O           | No                | Yes                   | Yes                     | Yes                            |

| U-O2P           | No                | Yes                   | No                      | No                             |

| U-O/U-R         | Yes               | Yes                   | Yes                     | Yes                            |

| U-R2P           | No                | Yes                   | No                      | No                             |

| U-R2S           | No                | Yes (see note)        | Yes                     | Yes                            |

| U-R2            | Yes               | No                    | No                      | No                             |

NOTE: The POTSA-C adapter needs power for signalling conversion and will usually be locally powered if it is collocated with the PSE, but it needs access to RPF to detect its presence and may optionally be powered by RPF.

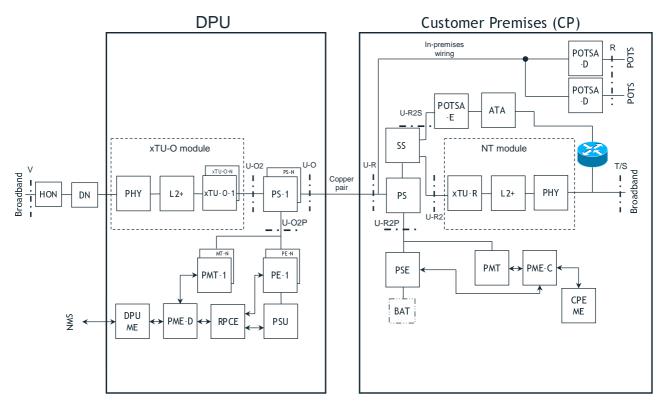

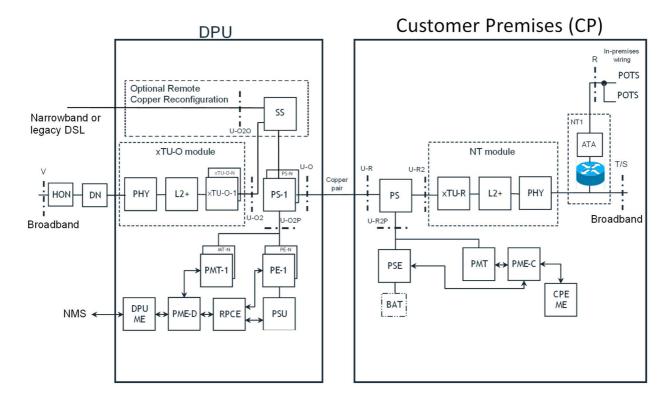

# 5.5 Reverse Power Feed Architecture with Baseband POTS from the Exchange Sharing the in-premises Wiring (RPFA-EXPSW)

The functional reference model of the reverse power feed architecture with baseband POTS from the exchange sharing the in-premises wiring (RPFA-EXPSW) is shown in Figure 5 and the associated reference points are detailed in Table 4. In this application, each POTS device connected to the in-premises network is connected to an individual POTSA-D which provides POTS signalling translation. This reference model is used when a traditional voice solution is utilized but an analogue POTS presentation is required over the in-premises wiring including all extension wiring.

Figure 5: RPFA-EXPSW Reference Model

Reference Point Reverse Power Out of band POTS **Broadband Signals Analog Voice** Signalling Feed **Signals** U-O2 Yes Yes No No U-020 Yes Yes No Yes U-O2P No Yes No No Yes (see note) U-O/U-R Yes Yes Yes U-R2P No No Yes No U-R2 Ye<u>s</u> No No No NOTE: RPF provides power for signalling conversion.

**Table 4: RPFA-EXPSW Reference Points**

It should be noted that the use cases for RPFA-EXP and RPFA-EXPSW may be combined so that POTSA-C and POTSA-D may both be present.

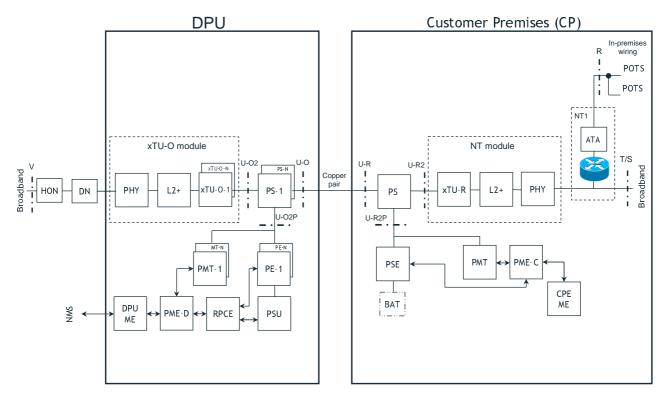

# 5.6 Reverse Power Feed Architecture with Derived POTS (RPFA-DRP)

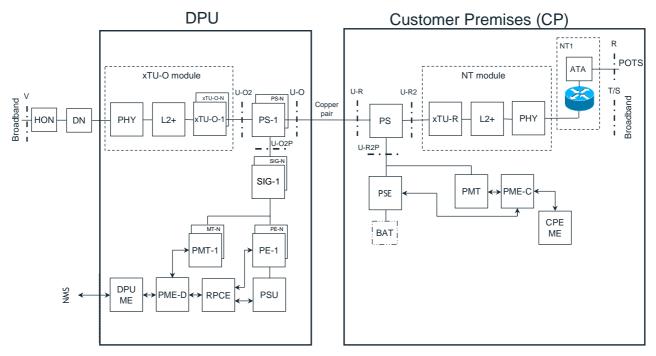

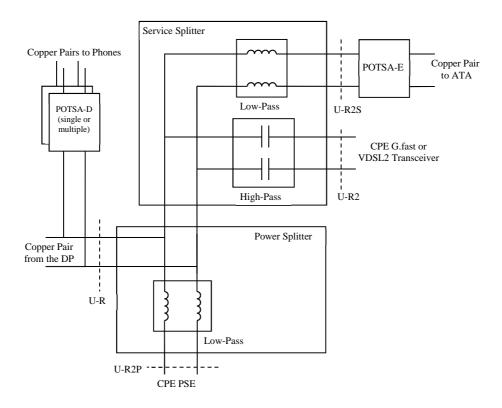

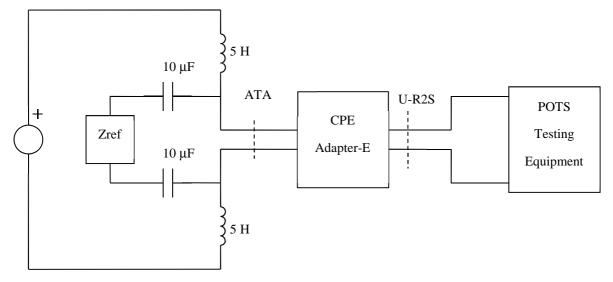

The functional reference model of the reverse power feed architecture with derived POTS (RPFA-DRP) is shown in Figure 6 and Figure 7 and the associated reference points are detailed in Table 5.

Similar to the RPFA-EXP architecture defined in clause 5.4, this option includes two different variants. Figure 6 illustrates the case when the CPE (Power Splitter (PS), Power Source Equipment (PSE) and NT module) may be located anywhere on the in-premises wiring while a single analogue POTS interface is available on the dedicated line (i.e. POTS service uses one wire pair while the DSL service uses another wire pair). The second variant is shown in Figure 7. This illustrates the case where the CPE is installed at the master-socket location and multiple POTS interfaces are distributed over the in-premises wiring. In this architecture, an analogue presentation of a VoIP service is provided at the CPE via an Analogue Terminal Adapter (ATA). Other application models are possible, for example where the ATA is connected to a cordless phone or a wireless phone device. The ATA can be integrated with the router in the same physical box NT1, or with the NT module. Such a scheme is inherently simpler than the POTS solutions described in clause 5.4 because there is no requirement for service splitter and POTS Adapters. However, this solution proves to be the most difficult to arrange for POTS failover during power outages at the CPE. Such a solution is dependent upon local battery power at the CPE being able to also power the remote node (albeit the remote node may be operating in a low-power mode).

Figure 6: RPFA-DRP Reference Model with derived POTS and a single POTS port

Figure 7: RPFA-DRP Reference Model with derived POTS distributed over In-Premises Wiring

**Reference Point Broadband Signals Reverse Power Feed Analogue Voice Signals** U-02 Yes Yes No Yes U-02P No No U-O/U-R Yes No Yes U-R2P Yes No No U-R2 Yes No No

**Table 5: RPFA-DRP Reference Points**

# 5.7 Reverse Power Feed Architecture with Derived POTS Sharing the in-premises Wiring (RPFA-DRPSW)

The functional reference model of the reverse power feed architecture with derived POTS sharing the in-premises wiring (RPFA-DRPSW) is shown in Figure 8 and the associated reference points are detailed in Table 6. In this application, POTS is carried as a derived voice stream within the broadband data. The voice stream is extracted via a router and then presented to a POTS Adapter via an ATA. The voiceband POTS signal is injected onto the in-premises wiring via the voice-frequency path through the Service Splitter (SS). Because there is DC powering present on the in-premises wiring, it is not possible to include DC POTS signalling and therefore a POTSA-D is required for every POTS device that is not collocated with the NT module.

Figure 8: RPFA-DRPSW Reference Model

**Table 6: RPFA-DRPSW Reference Points**

| Reference Point | Broadband<br>Signals | Reverse Power Feed | Analogue Voice<br>Signals | Out Of Band POTS<br>Signalling |

|-----------------|----------------------|--------------------|---------------------------|--------------------------------|

| U-O2            | Yes                  | Yes                | No                        | No                             |

| U-O2P           | No                   | Yes                | No                        | No                             |

| U-O/U-R         | Yes                  | Yes (see note 1)   | Yes                       | Yes                            |

| U-R2P           | No                   | Yes                | No                        | No                             |

| U-R2S           | No                   | Yes (see note 2)   | Yes                       | Yes                            |

| U-R2            | Yes                  | No                 | No                        | No                             |

NOTE 1: RPF provides power for signalling conversion.

NOTE 2: The POTSA-E adapter needs power for signalling conversion and is usually locally powered if it is collocated with the PSE, but it needs access to RPF to detect its presence and may optionally be powered by RPF.

It should be noted that the use cases for RPFA-DRP and RPFA-DPRSW may be combined so that a POTS port and POTSA-D may both be present.

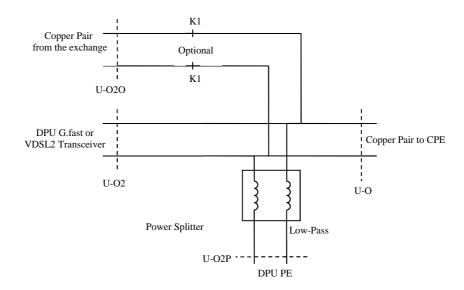

# 5.8 Reverse Power Feed Architecture without POTS and with Broadband Bypass (RPFA-NOPBB)

The functional reference model of the reverse power feed architecture without POTS on the same pair and with Broadband Bypass (RPFA-NOPBB) is shown in Figure 9 and the associated reference points are detailed in Table 7. This scenario is based on the reference model RPFA-NOP without POTS.

A stateless switching function SF in the DPU connects the xTU-R in the CPE either with the xTU in the CO/cabinet or with the xTU-O in the DPU. The SF may include filter and impedance adapting means to prevent the leakage of noise into and from the U-O2 interface and impedance changes impacting the crosstalk characteristics by changing the switch positions. Stateless means that the NMS does not control the states of the switch. In the default position, the switch connects the xTU in the CO/cabinet with the xTU-R. When a PSE is connected and reverse power feeding starts, the power management in the DPU sends a signal to the Switch Control Function (SCF). The Switch Control Function triggers the switch in order to switch over from the xTU in the CO/cabinet to the xTU-O in the DPU. Then, the xTU-R is connected with the xTU-O in the DPU. The behaviour of the switch when the PSE is not present for a time period T, shall be defined by the operator.

Figure 9: RPFA-NOPBB Reference Model

Out of band POTS **Reference Point Broadband Signals Reverse Power Analog Voice** Feed Signalling Signals U-02 Yes Yes No No U-020 No No No Yes U-O2P No Yes No No U-O/U-R Yes Yes No No U-R2P No Yes Νo No U-R2 Yes No No No

**Table 7: RPFA-NOPBB Reference Points**

# 6 Reverse Power Feed Start-Up Protocol

#### 6.1 Introduction

#### 6.1.1 General

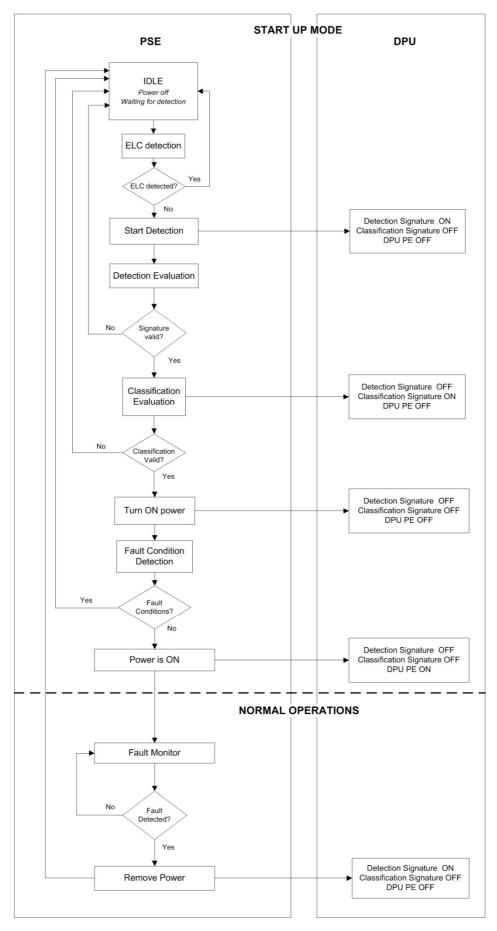

As shown in clause 5, Reverse Power Feed can be applied either in conjunction with a baseband POTS service from a CO, or with a derived POTS service, or without any POTS service.

In any scenario, a procedure shall be followed to guarantee proper interaction between the elements of the RPF system (DPU - PSE - POTS Adapters in the in-premises network). The procedure shall allow a proper start-up of RPF, and should cover all further states of the RPF system (operation, shut down, error conditions).

Powering DPUs over copper lines implies additional requirements because the power source is remote and the power feeding may co-exist with the POTS service, whether this is exchange based POTS (RPFA-EXP, RPFA-EXPSW) or derived POTS (RPFA-DRP, RPFA-DRPSW). For example, if reverse powering is present on the in-premises network it is important to detect directly connected off-hook phones and prevent them from becoming a safety hazard. If a directly connected off-hook telephone is detected, a back-off mechanism shall be initiated for the reverse powering.

The following power source requirements apply (clause 8.2 of TR-301 [4]):

- 1) The PSE of a single active line shall be able to power its DPU in both mains-powered and battery-powered (when available) operation.

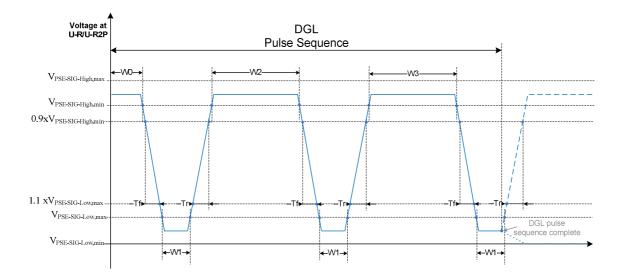

- 2) The PSE shall send a Dying Gasp indication to the DPU after it has lost both mains and battery power (if available) and before it removes power from the line.

- 3) The PSE shall remove power from a line upon the detection of a fault condition.

- 4) During normal operation, if any of these fault conditions occur, the PSE shall remove power and return to the startup procedure:

- a) Presence of an open circuit.

- b) Presence of a short circuit.

- c) Presence of an off-hook phone.

- 5) In the case where the PSE detects a fault condition, the PSE shall not inject full power on the line.

- 6) The PSE shall verify that all of the following conditions are met, before injecting full power:

- a) Absence of an open circuit.

- b) Absence of a short circuit.

- c) Absence of a POTS Exchange (foreign) DC voltage on the line.

- d) Absence of an off-hook phone.

- e) Detection of a DPU that supports reverse powering.

- f) Correct matching of the PSE RPF Class with the DPU RPF Class.

- 7) The PSE shall power the DPU independent of the polarity on the line.

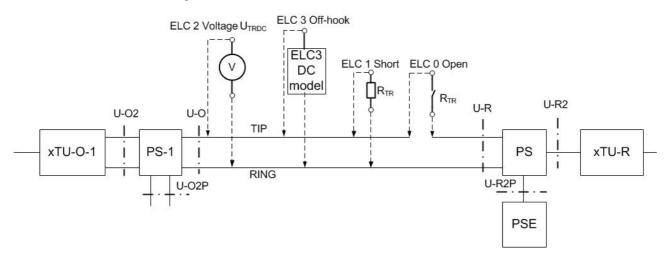

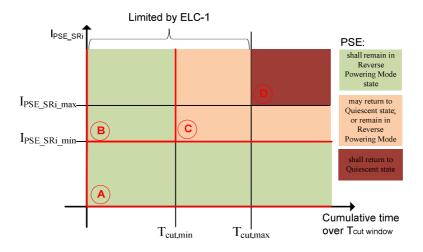

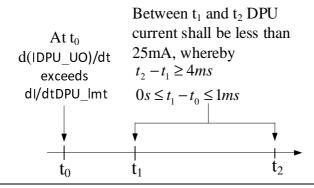

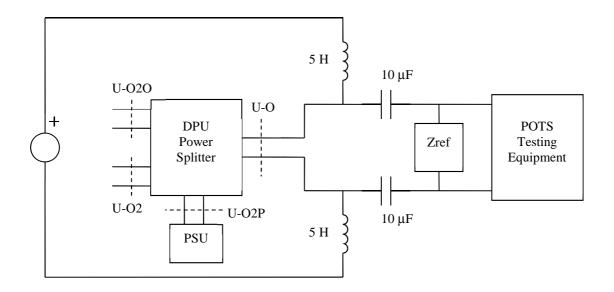

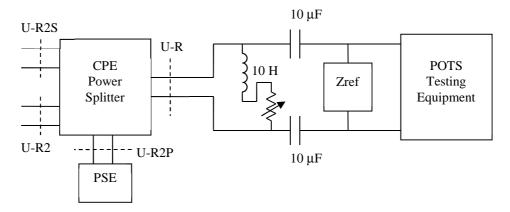

The equivalent network model of the above line related fault conditions (further referred to as the Error Line Conditions ELC 0 to ELC 3) is shown in Figure 10.

Figure 10: Illustration of an Error Line Conditions network model

The Error Line Condition parameters and detection criteria for the ELC network model are defined in Table 8.

**Table 8: Error Line Condition Parameters and Detection Criteria**

| <b>Error Line Condition</b>                                                                           | Description          | Parameter                                                                | Detection Criteria                                 |  |

|-------------------------------------------------------------------------------------------------------|----------------------|--------------------------------------------------------------------------|----------------------------------------------------|--|

| ELC 0                                                                                                 | Open tip-to-ring     | $R_{Emin} = 1 M\Omega$                                                   | R <sub>TR</sub> ≥ R <sub>Emin</sub> for a duration |  |

|                                                                                                       |                      | C <sub>Emax</sub> = 100 nF                                               | exceeding 300 ms (see note)                        |  |

|                                                                                                       |                      |                                                                          | $C_{TR} \le C_{Emax}$                              |  |

| ELC 1                                                                                                 | Short tip-to-ring    | $R_{Emax} = 140 \Omega$                                                  | $R_{TR} \le R_{Emax}$                              |  |

| ELC 2                                                                                                 | POTS Exchange        | U <sub>TRDCEmax</sub> = 3 V  U <sub>TRDC</sub>   ≥ U <sub>TRDCEmax</sub> |                                                    |  |

|                                                                                                       | (foreign) DC voltage |                                                                          |                                                    |  |

| ELC 3                                                                                                 | Off-hook phone       | Measured voltage and current in the range below the                      |                                                    |  |

|                                                                                                       |                      | upper limit of the DC characteristics defined in Table 9                 |                                                    |  |

| NOTE: This duration is set such that the definition of ELC 0 does not overlap with the Maintain Power |                      |                                                                          |                                                    |  |

| Signature definition as defined in note 4 of Table 41.                                                |                      |                                                                          |                                                    |  |

NOTE: Due to the definition of parameters, definite detection of ELC 1 or ELC 3 may be ambiguous.

The RPF start-up protocol shall use the detection criteria listed in Table 8 to ensure detection of Error Line Conditions (ELC).

The upper limits of the off-hook phone DC characteristics are specified in Table 9 according to clause 4.7.1 of ETSI ES 203 021-3 [8].

Table 9: Upper limits of the Off-hook phone DC voltage/current characteristics

|       | Point                                                                                                           | Voltage (V) | Current (mA) |

|-------|-----------------------------------------------------------------------------------------------------------------|-------------|--------------|

|       | Α                                                                                                               | 9           | 0            |

|       | В                                                                                                               | 9           | 20           |

|       | С                                                                                                               | 14,5        | 42           |

|       | D                                                                                                               | 40          | 50           |

|       | Е                                                                                                               | 60          | 56           |

| NOTE: | NOTE: Linear interpolation of voltage in function of current shall be used to obtain values between points A-E. |             |              |

#### 6.1.2 Start-up in presence of MELT signature

The RPF start-up protocol shall operate irrespective of the presence of MELT signatures located at the CPE side.

Table 10 defines the MELT signatures located at the U-R interface for which the operability of the RPF start-up protocols shall be provided.

- A PSE that supports the Metallic Detection based Start-Up protocol (MDSU) shall start up with the RC type MELT signature, defined in Table 10, having time constant  $t = R \times C \le 49$  ms.

- A PSE supporting POTS Remote copper reconfiguration Protocol (PRP), an optional extension of the MDSU defined in clause 6.2.5, shall start up with the RC type MELT signature, defined in Table 10, having time constant  $t = R \times C \le 49$  ms and a resistive part exceeding  $4 \text{ k}\Omega$ .

**MELT** signatures ## Comments DR type Specified in TR-286 [5] R Nominal value Component 470 kΩ ± 1 %U<sub>F(D)</sub>  $0.7 \text{ V (at If} = 10 \text{ mA)} \pm 0.1 \text{ V}$ 2 ZRC type Specified in TR-286 [5] D1 D2 R Component Nominal value  $100 \text{ k}\Omega \pm 1 \%$ 470 nF ± 1 %  $U_{Z(D1)}$ 6,8 V ± 5 % @ 50 µA 6,8 V ± 5 % @ 50 µA U<sub>Z(D2)</sub> RC type 3 Component Nominal value  $20 k\Omega \pm 1 \%$ 2,2 µF ± 10 %

**Table 10: MELT SIGNATURES**

# 6.2 Metallic Detection based Start-Up (MDSU) Protocol

#### 6.2.1 Signature detection

The Metallic Detection based Start-Up (MDSU) protocol is applicable to three architecture scenarios defined in clause 5, Table 1; "without POTS" (RPFA-NOP), "with derived POTS" (RPFA-DRP) and "without POTS and with Broadband Bypass" (RPFA-NOPBB). After checking for the absence of typical POTS line conditions (off-hook, foreign DC voltage from the POTS Exchange) and the short and open line condition (a tip-to-ring short and open), the procedure allows for a proper start-up of the RPF.

A metallic detection based start-up method provides a convenient and reliable way to prevent supplying power to off-hook phones since it inherently tests line signature resistance which is much larger than the resistance of any off-hook phones.

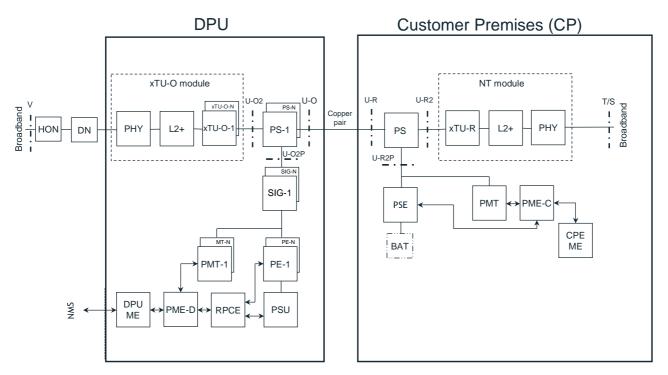

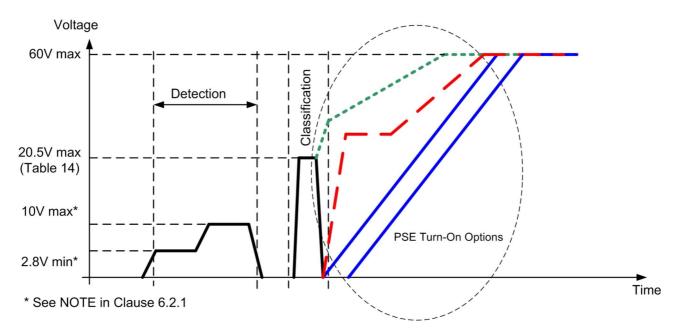

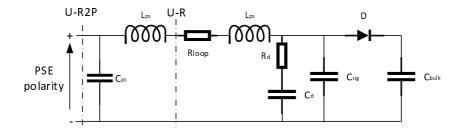

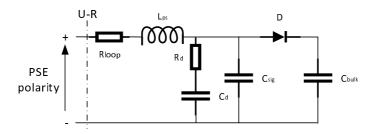

The MDSU protocol is based on detection of a resistive signature located in the DPU, that is a 25 k $\Omega$  resistor R<sub>SIG</sub> bridged across the tip- and ring-wire. The detection signature is part of the functional block SIG, as shown in Figure 11, Figure 12 and Figure 13. The PSE, located in the customer premises, probes the DPU in order to detect a valid DPU detection signature and applies the power to the DPU after successful verification of the line conditions listed under requirement 6) in clause 6.1 and classification of the classification signature. After the DPU is powered up, the detection and classification signatures may be disconnected to save the PSE power.

The class verification function provides an additional level of confidence in correct DPU and PSE mutual identification. In addition to a valid detection signature, the DPU shall provide a signature classification which is represented by a specific current level.

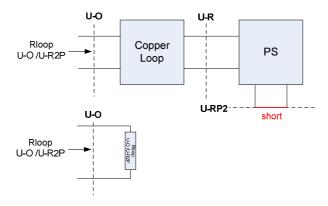

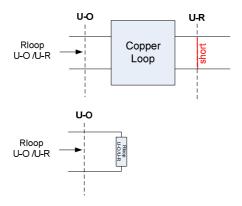

Figure 11: RPFA-NOP reference model with the DPU signature

Figure 12: RPFA-DRP reference model with the DPU signature

Figure 13: RPFA-NOPBB reference model with the DPU signature

The signature detection process is performed by applying a small current-limited voltage to the device between tip and ring, while measuring the tip-ring DC resistance ( $R_{TR}$ ) and capacitance ( $C_{TR}$ ), applied by the DPU device. The method to measure resistance  $R_{TR}$  and capacitance  $C_{TR}$  is vendor discretionary. The measurement method shall not violate the electrical specifications listed in Table 11.

NOTE: One possible approach is shown below. In evaluating the presence of a valid DPU signature, the PSE should make at least two measurements with voltage values at the PSE (V<sub>PSE</sub>) that create at least a 1 V difference between test points. The detection voltage measured at the PSE (V<sub>PSE</sub>) should typically be between 2,8 V and 10 V with a valid DPU detection signature connected.

The resistance is calculated as:

$$\mathbf{R}_{SIG} = \frac{v_{PSE2} - v_{PSE1}}{i_{PSE2} - i_{PSE1}}$$

where:

- V<sub>PSE1</sub> and V<sub>PSE2</sub> are the first and second voltage measurements made by the PSE, respectively.

- I<sub>PSE1</sub> and I<sub>PSE2</sub> are the first and second current measurements made by the PSE, respectively.

The PSE should control the slew rate of the probing detection voltage when switching between detection voltages to be less than 0,1  $V/\mu s$ . The voltage or current measurement should be taken after  $V_{PSE}$  has settled to within 1 % of its steady state condition.

The signature detection process also includes measuring a foreign DC voltage (U<sub>TRDC</sub>) between TIP and RING.

Table 11: Measurement signals for measuring R<sub>TR</sub> and C<sub>TR</sub>

| Measured parameter                  | Measurement Voltage, V <sub>MEAS</sub> , at U-R (PSE with integrated PS) / U-R2P (PSE with external PS) | Measurement current, I <sub>MEAS</sub> ,<br>through U-R2P interface |

|-------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| R <sub>TR</sub> and C <sub>TR</sub> | 0 < V <sub>MEAS</sub> ≤ 30 V                                                                            | 0 < I <sub>MEAS</sub> ≤ 5 mA                                        |

The PSE shall apply power to the DPU if the following condition is satisfied:

A valid DPU signature is detected and none of the error line conditions ELC 0 to ELC 3 defined in Table 8 occur.

The PSE shall not apply power to the DPU if the following condition is satisfied:

Non-valid DPU signature is detected or at least one of the error line conditions ELC 0 to ELC 3 defined in Table 8 occur.

Note that the PSE may accept or reject a signature resistance in the band between  $R_{NVlow}$  and  $R_{Vmin}$ , and in the band between  $R_{Vmax}$  and  $R_{NVhigh}$  (see Table 12).

In normal operation, the PSE shall remove power and return to the startup procedure if any of the following error line conditions occur:

- Presence of an open circuit

- Presence of a short circuit

- Presence of an off-hook phone

These are listed in Requirement 5) of clause 6.1.

The PSE detection criteria for the DPU signature is defined in Table 12.

Table 12: PSE Detection criteria for the DPU signature

| DPU signature | Parameter                                                        | Detection Criteria                        |

|---------------|------------------------------------------------------------------|-------------------------------------------|

| Valid         | $R_{Vmin} = 19 \text{ k}\Omega; R_{Vmax} = 26,5 \text{ k}\Omega$ | $R_{Vmin} \le R_{TR} \le R_{Vmax}$        |

|               | $C_{Vmax} = 150 \text{ nF}$                                      | $C_{TR} \le C_{Vmax}$                     |

| Non-valid     | $R_{NVhigh} = 33 k\Omega$ ; $R_{NVlow} = 15 k\Omega$             | R <sub>TR</sub> < R <sub>NVlow</sub> , or |

|               | $C_{NV} = 10 \mu F$                                              | $R_{TR} > R_{NVhigh}$ , or                |

|               |                                                                  | C <sub>TR</sub> ≥ C <sub>NV</sub>         |

The electrical characteristics of the DPU signature shall comply with Table 13.

Table 13: Electrical characteristics of DPU signature

| Parameter                                            | Symbol                  | Units | Min  | Max  |

|------------------------------------------------------|-------------------------|-------|------|------|

| Resistor                                             | Rsig                    | kΩ    | 23,7 | 25,5 |

| Capacitor (in parallel with signature resistor)      | C <sub>SIG</sub>        | μF    | 0,05 | 0,12 |

| Input voltage at which the DPU removes the signature | V <sub>Disconnect</sub> | V     | 10,1 | 12,8 |

| resistance                                           |                         |       |      |      |

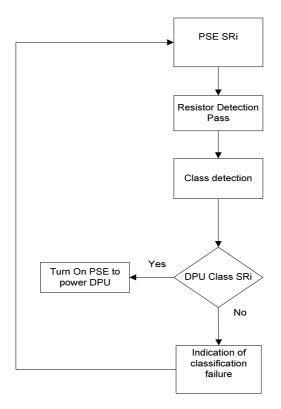

### 6.2.2 DPU classification using MDSU protocol

The key objectives of the DPU classification are:

- To establish mutual identification of PSE and DPU as an enhanced validation mechanism on top of the detection mechanism. This addresses the scenario in which a combination of connected equipment (phones, fax machines, etc.) would have the same signature as those of a valid DPU.

- To provide power level interoperability criteria between PSE power classes and DPU power consumption.

In addition to a valid detection signature, the DPU shall provide the characteristics of a classification signature as specified in Table 14. A DPU shall present one, and only one, classification signature during classification.

Table 14: DPU classification signature

| DPU class | Conditions          | Class min current | Class max current |

|-----------|---------------------|-------------------|-------------------|

| Class SR1 | Voltage from 14,5 V | 9 mA              | 12 mA             |

| Class SR2 | to 20,5 V at U-O    | 17 mA             | 20 mA             |

| Class SR3 | interface           | 26 mA             | 30 mA             |